电子管技术开启了电子工业, 迎来电子时代. 但这些发光管占用了很大的空间, 消耗大量能源. 早在上个世纪40年代便开始了减小电子产品个头的竞赛:1947发明的晶体管触发了在更小的封装提供更强功能的电子设备的演绎.

1965年,英特尔的创始人之一戈登摩尔(Gordon Moore)预言,集成电路上能被集成的晶体管数目,将会以每18个月翻一番的速度稳定增长,并在今后数十年内保持着这种势头.—摩尔定律(也被称为电子电脑第一定律).过去的40多年,证实了几乎两年翻一番的准确性, 该预言也成为半导体工业的基准. 一块芯片一个门已发展成集成电路,微处理器已是含有数于亿计的门的芯片.

晶硅工艺的出现使追求更大的半导体密度趋势一直延续, 从90纳米到60纳米再到45纳米.

微小的封装里具有强大的计算功能迎来了多核处理器和超大容量的闪存;单板计算机能被镶到各种各样的设备里;单块芯片能够实现母板的功能;将系统装入单晶片已成为现实.

所有这些导致系统速度,内存容量,处理能力的剧增. 产品变得越来越小,功能却越来越强. 曾经是价值数百万美元,房子大小的商务机器变成到处可买的手提工具. 计算功能,通讯功能和娱乐功能的融合产生诸如iphone这样的产品,这在以前恐怕只有在科幻小说里才能出现.

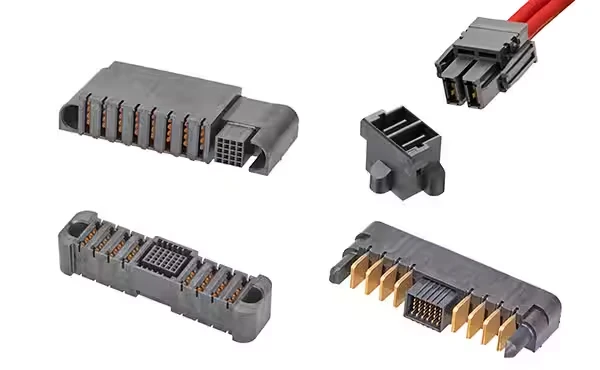

电子系统个头大小的收缩影响到产品里每个零配件,包括连接器. 连接器的post的尺寸从0.31英寸X 0.62英寸降到0.025英寸X0.025英寸,中心距由0.56英寸降到0.1英寸. 今天柔性电路板连接器的端子能做到0.3mm,甚至更小. 中心距更小的连接器不仅能装入到更小的产品,空间利用率也更高(每立方毫米所容纳的电路).

这一代的微处理器已超出1200pin脚,若没有零插入力高密度的连接器是不可能连接的. 芯片上活动单元相互之间的物理距离更接近,有利于提高处理速度,但封装的密度也更大.

连接器与电路板的连接技术也不断发展,来应对更高的端子密度. 穿孔的波峰焊已改进到表贴方式. 现在的很多连接器提供多种连接方式(穿孔,软干涉/compliant pin, 表贴)的版本. 如高密度的背板连接器是通过锡球焊到电路板上的.

原来2.0mm 的背板连接器慢慢被新一代高速高密度(间距1.5mm或更小),融入地线层,端子利用差分对技术的连接器取代. 近年来,FCI和Tyco分别发行了新款超高密度的背板连接器. 泰科的Z-Pack Slim UHD密度高达每平方厘米55 pin而法码通的ZipLine则每英寸长度能容纳101对差分信号.

端子中心距的降低使系统设计者能够缩小子板间的距离,使设备能增添更多子板或设备外形更小. 外形更矮的连接器有利于空气流通,带走热量,提高设备工作环境的温度范围.

能够利用子板间的空间使背板模块结构非常吸引人,高度超低的连接器允许平行的电路板以极小的间隙被连接.

手提的娱乐兼数据储存数码产品必须足够小和足够轻,这样几乎没有什么空间留给I/O连接器, 标准的RS-232连接器几乎完全被标准的,mini, 和micro USB界面取代.

娱乐的电子消费产品变得越来越先进,往往带有高清电视和环绕立体声功能. 当用户因为无法连接手提高清电视信号而懊恼时HDMI连接器便问世,它提供了更高的空间利用率和更宽的带宽, 当然也就更好的视频效果.

硬盘连接器也从并联的40pin ATA发展到串联的7pin ATA, 这不仅增加了带宽也更便于安装及利于散热.

在柔性电路板和极细电缆组件也不难找到小型微型连接器的影子.

目前市面上已出现0.7mm高度的表贴连接器.

电路密度不断提高的趋势必然对连接器产业压力. 传统的在注塑塑胶件放置金属冲压成形的端子的做法必然会达到它们的极限. 环境法规禁止连接器端子镀层含有铅元素成分的规定使中心距小的镀锡端子由于锡须的形成产生短路的隐患. 可替代的连接技术,如导电聚合物,金属化颗粒等也许允许更小的中心距,但每项新技术都不可避免面临系列的挑战.

用新兴的纳米技术制造的新的连接器结构也许能为新一代高密度连接系统提供出路, 纳米材料(如纳米碳管/carbon nanotubes)连接器在微米级的中心距具有很高导电率.

电子工业从它一开始便展现小型化的趋势,这种潮流继续引领连接器产业小型化微型化高密度化.